Normal Supply

Normal SupplyCan generate eight non integers

Related frequencies range from 2.5 kHz to 200 MHz

I2C user-defined configuration

Accurate frequency synthesis output for each position (0ppm error)

High linearity VCXO

Optional clock input (CLKIN)

Low output cycle jitter:<70ps pp

Configurable spread spectrum can be selected at each output terminal

Fixed frequency crystal: 25 or 27 MHz

Support static phase offset

Programmable rise/fall time control

Separate power pin

Core VDD: 2.5 or 3.3 V

Output VDDO: 1.8, 2.5, or 3.3 V

Excellent PSRR eliminates external interference and power filtering

Very low power consumption

Adjustable output delay

PCIE Gen 1 compatibility

Support HCSL compatible swing

Package: MSOP-10 (0.118 ", 3.00mm wide)

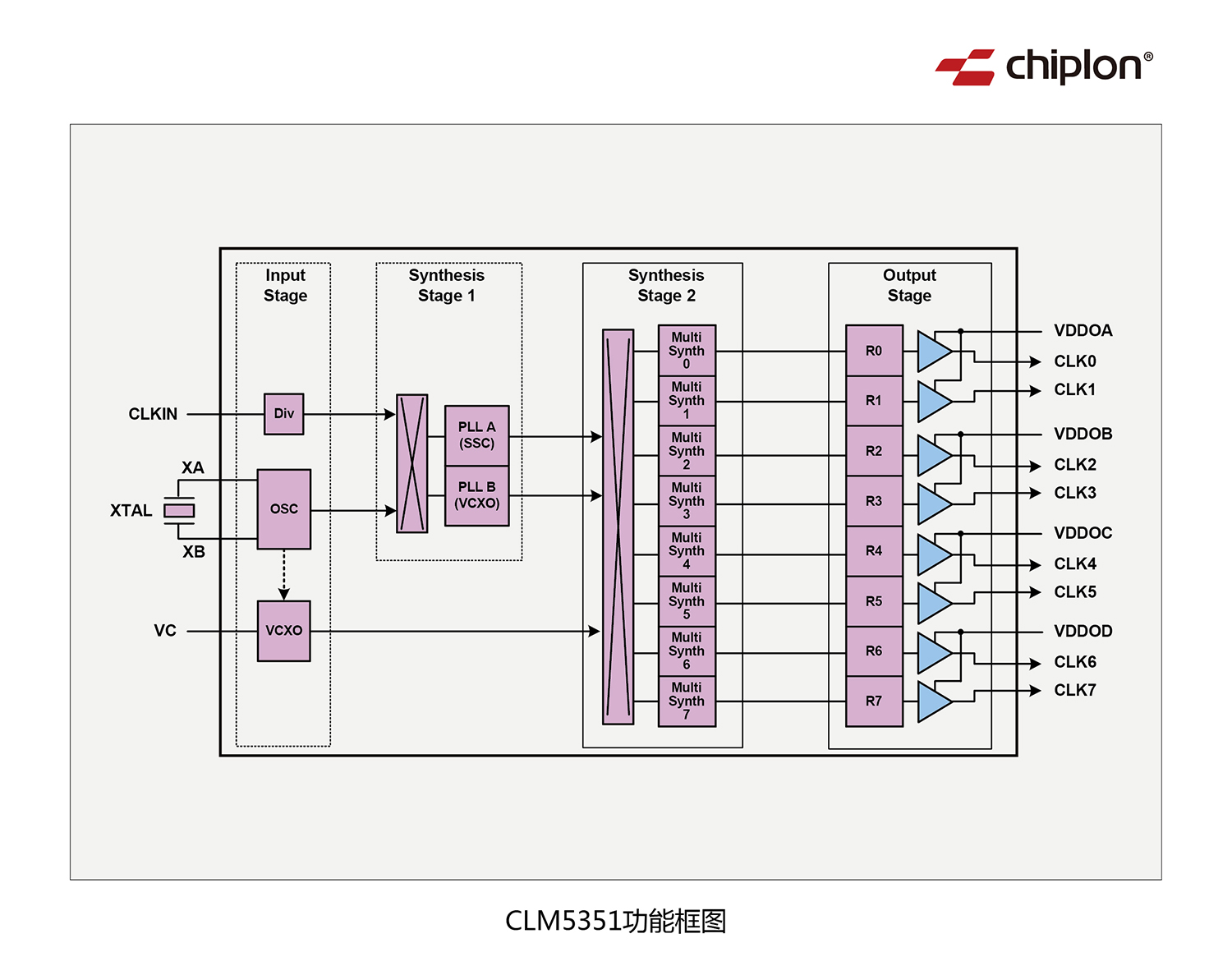

CLM5351 is a high-performance I2C configurable clock generator developed by Chiplon. It is an ideal replacement for crystals, crystal oscillators, VCXOs, phase-locked loops (PLLs), and is suitable for use in cost-sensitive applications where fan-out buffers are required. Based on PLL/VCXO + high-resolution MultiSynth fractional divider, CLM5351 can generate any frequency up to 200 MHz on each chip with an output error of 0 ppm. The product can directly pin to pin replace similar international products without the need to change the circuit board or system software, achieving complete compatibility and replacement. Chiplon Microelectronics has developed its own testing plan to ensure that the factory products meet or even exceed the original specifications, supporting industrial grade working temperatures (-40 ℃~85 ℃). Competing product: SI5351A-B-GT

Can generate eight non integers

Related frequencies range from 2.5 kHz to 200 MHz

I2C user-defined configuration

Accurate frequency synthesis output for each position (0ppm error)

High linearity VCXO

Optional clock input (CLKIN)

Low output cycle jitter:<70ps pp

Configurable spread spectrum can be selected at each output terminal

Fixed frequency crystal: 25 or 27 MHz

Support static phase offset

Programmable rise/fall time control

Separate power pin

Core VDD: 2.5 or 3.3 V

Output VDDO: 1.8, 2.5, or 3.3 V

Excellent PSRR eliminates external interference and power filtering

Very low power consumption

Adjustable output delay

PCIE Gen 1 compatibility

Support HCSL compatible swing

Package: MSOP-10 (0.118 ", 3.00mm wide)

Audio/Video equipment

Printers, scanners, projectors

Portable instruments

Laser rangefinders

Home gateways

Network/Communication

Servers, storage