In Development

In DevelopmentOutput frequency range: 35 MHz to 4400 MHz

Decimal N-division frequency synthesizer and integer N-division frequency synthesizer

VCO with low phase noise

Programmable 1/2/4/8/16/32/64 frequency division output

Typical RMS jitter: 0.3 ps rms

EVM: 0.4% (typical value, 2.1 GHz)

Power supply: 3.0 V to 3.6 V

Logical compatibility: 1.8 V

Programming dual-mode prescaler: 4/5 or 8/9

Programmable output power

RF output mute function

Three wire serial interface

Analog and digital lock detection

Quick lock mode within wide bandwidth

Week jump reduction

Package: LFCSP-32 (5x5)

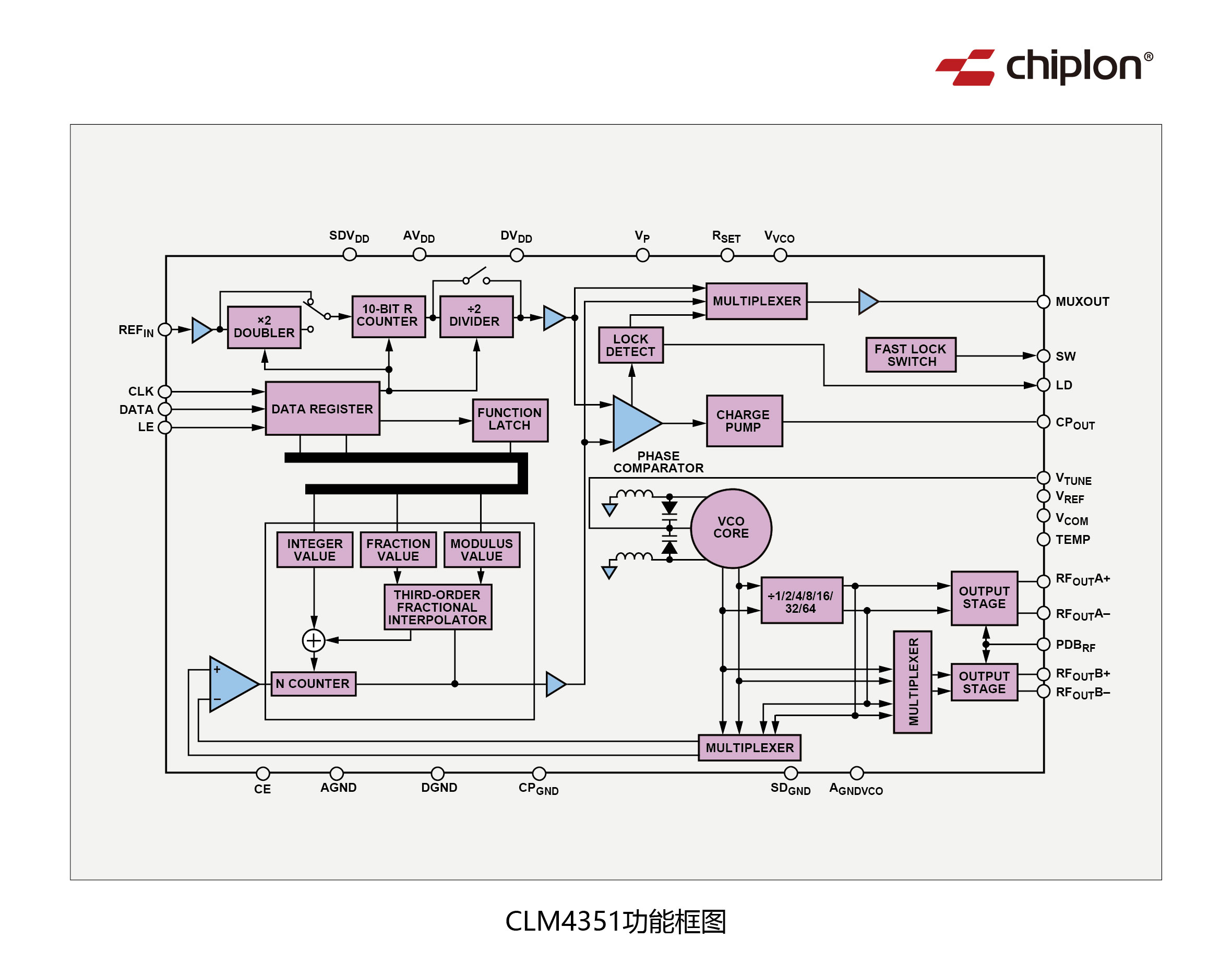

CLM4351 is an external loop filter developed by Chiplon, which can be combined with a reference frequency to form a decimal N-division or integer N-division phase-locked loop (PLL) frequency synthesizer. This device integrates a voltage controlled oscillator (VCO) with a fundamental output frequency range covering 2200 MHz to 4400 MHz; With the 1/2/4/8/16/32/64 frequency divider circuit, users can further obtain RF output frequencies as low as 137.5 MHz. For application scenarios that require isolation, the RF output stage supports mute function, which can be controlled through pins or software dual control; Simultaneously providing auxiliary RF output, which can be turned off when idle to reduce power consumption. All on-chip registers are controlled through a simple three wire interface, and the device is powered by 3.0 V to 3.6 V, which can also be turned off when idle. The product can directly pin to pin replace similar international products without the need to change the circuit board or system software, achieving complete compatibility and replacement. Chiplon Microelectronics has developed its own testing plan to ensure that the factory products meet or even exceed the original specifications, supporting industrial grade working temperatures (-40 ℃~85 ℃). Competing product: ADF4351BCPZ

Output frequency range: 35 MHz to 4400 MHz

Decimal N-division frequency synthesizer and integer N-division frequency synthesizer

VCO with low phase noise

Programmable 1/2/4/8/16/32/64 frequency division output

Typical RMS jitter: 0.3 ps rms

EVM: 0.4% (typical value, 2.1 GHz)

Power supply: 3.0 V to 3.6 V

Logical compatibility: 1.8 V

Programming dual-mode prescaler: 4/5 or 8/9

Programmable output power

RF output mute function

Three wire serial interface

Analog and digital lock detection

Quick lock mode within wide bandwidth

Week jump reduction

Package: LFCSP-32 (5x5)

Wireless infrastructure

Testing equipment

Wireless Local Area Network (LAN), cable TV equipment

Clock generation